Algoritma kriptografi AES merupakan algoritma yang sering digunakan dalam menjaga kerahasiaan data. Kerahasiaan data merupakan parameter utama pengamanan data di berbagai sistem. Keamanan data dapat dicapai dengan mengkolaborasikan algoritma AES dengan algoritma kriptosistem lainnya. Oleh karena itu,perangkat keras pengeksekusi algoritma AES dengan sumber daya terbatas menjadi sangat penting.

Penelitian ini mengusulkan rancang bangun purwarupaperangkat keras untuk eksekusi algorima AES yang mengutamakan pemakaian sumber daya optimalmenggunakan FPGA tanpa mengorbankan kecepatan eksekusi. Pengoptimalan sumber daya ditempuh dengan merancang perangkat keras untuk enkripsi dengan dekripsi yang saling berbagi sumber daya, menggunakan arsitektur iteratif pada level putaran, arsitektur pipeline pada level transformasi, dan lebar data 32 bit.

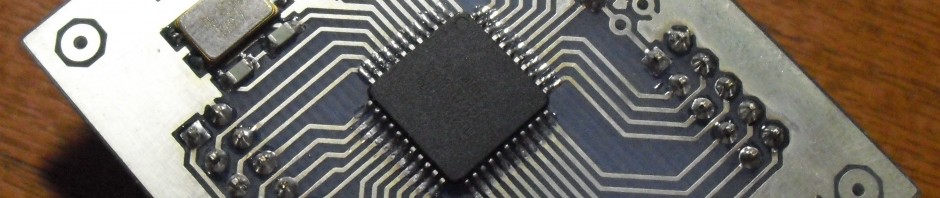

Purwarupa perangkat keras pada penelitian ini menggunakan FPGA Xilinx Spartan®-6 Seri (XC6LX16-CS324) hasil pemodelan telah berhasil melakukan proses enkripsi dan dekripsi. Efisiensi perangkat keras yang dicapai adalah 1,94Mbps/Slice, sedangkan lewatan yang diperoleh adalah 308,96Mbps. Dengan pemakaian sumber daya hanya 6% dari yang tersedia pada FPGA.